DDRx仿真

仿真難點

- 走線密度大,顆粒數(shù)量多,運行速率高、時序裕量小,驅(qū)動種類多

仿真目的

- 指導(dǎo)Layout布局布線

- 項目調(diào)試中出現(xiàn)問題,通過仿真定位問題并提出改進(jìn)意見

- 測不到芯片內(nèi)部的信號,通過仿真對比外部測試數(shù)據(jù),模擬到芯片內(nèi)部的真實情況

仿真內(nèi)容

- 拓?fù)鋬?yōu)化,ODT調(diào)節(jié),驅(qū)動選擇,端接/串阻阻值調(diào)節(jié),時序分析,針對所有信號線進(jìn)行全通道仿真

仿真意義

- 指導(dǎo)Layout布局布線

- (LP)DDR3/4/5、GDDR6拓?fù)漕愋瓦x擇

- 低功耗要求時,能否關(guān)掉ODT也能正常工作

- (LP)DDR3/4/5、GDDR6在高密度、降成本(如減層、用普通工藝)時的設(shè)計指導(dǎo)

- HDI設(shè)計時無完整參考平面或者無法很好等長時布線指導(dǎo)

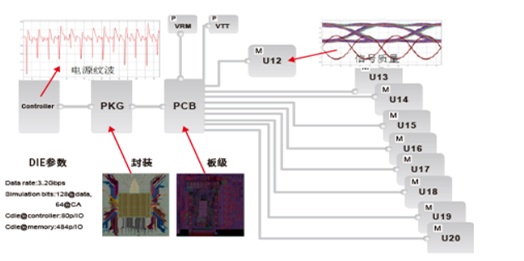

仿真對象

DDR(LPDDR)3/4/5全通道仿真

全通道SI+PI協(xié)同仿真

數(shù)據(jù)信號仿真

設(shè)計經(jīng)驗

一博科技每年15000款以上的設(shè)計經(jīng)驗,鑄就了業(yè)內(nèi)領(lǐng)先的DDR仿真技術(shù)

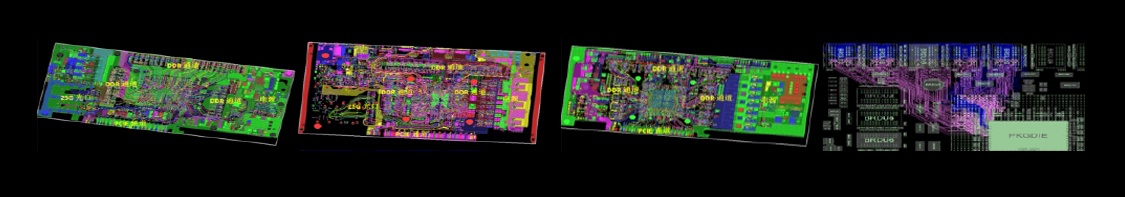

下圖為近年來熱門的AI人工智能的加速卡設(shè)計,高難度的設(shè)計和仿真幫助內(nèi)外AI公司快速推出其產(chǎn)品

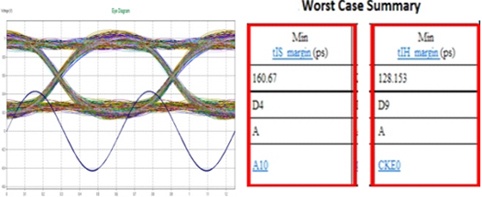

密集多通道LPDDR5算力卡,運行速率6400Mbps

仿真內(nèi)容

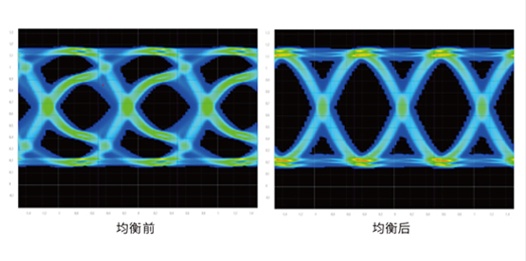

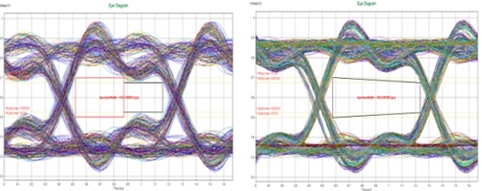

信號質(zhì)量仿真:

-仿真優(yōu)化前后結(jié)果對比

信號時序仿真:

-各組信號時序關(guān)系對應(yīng)

-時序窗口計算(建立/保持時間Margin)